| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | |||||

| 3 | 4 | 5 | 6 | 7 | 8 | 9 |

| 10 | 11 | 12 | 13 | 14 | 15 | 16 |

| 17 | 18 | 19 | 20 | 21 | 22 | 23 |

| 24 | 25 | 26 | 27 | 28 | 29 | 30 |

| 31 |

- drude

- 빛의 손실

- 라만 분석기

- 연속스펙트럼

- 라만 분석

- 에디슨의 패배

- Raman

- X선의 발견

- 특성스펙트럼

- 에너지 역학

- 재료과학

- X선 기초

- 재료열역학

- 화합물 반도체

- 그루데 이론

- 륀트겐

- 3 o'clock things

- X선

- 전기장이 가해진

- 전자의 속도

- 흡광

- 결정립

- von laue

- 슬립계

- 결정구조학

- X선 공학

- 라만 현상

- laue

- 일상

- 분해전단응력

- Today

- Total

공머생의 공부노트

Architecture and CMOS 본문

1. Von Neumann's architecture and Memory hierarchy

컴퓨터의 시작은 아날로그 계산기로부터 시작되었지만 현대의 대규모 연산장치의 구상도는 한 천재의 아이디어로부터 시작된다. 폰 노이만은 천재성으로 유명한 물리학자로서 핵폭탄 말고도 컴퓨터의 기본 구조를 구상하는데 큰 기여를 했다.

노이만이 제시한 컴퓨터의 구조는 Memory, Input, Processing unit, Output, Countrol unit으로 구성되고 각 구성요소는 우리가 컴퓨터를 사용하는데 그는 반도체도 거의 없던 시절 컴퓨터가 기본적으로 가져야 할 구조를 제시한다. 컴퓨터의 저장장치인 메모리에는 각 저장소와 그 위치가 있고 이 데이터를 중앙 연산장치로 불러오고 처리하는 방식으로 구성되었다.

MAR (Memory Address Register): 접근하고자 하는 메모리 주소를 저장함

MDR (Memory Data Register): 메모리에서 읽거나 쓸 데이터를 저장함

ALU (Arithmetic Logic Unit): 산술 및 논리 연산 수행

TEMP: 연산 중 임시 데이터 저장용 레지스터 또는 임시 버퍼

PC (Program Counter): 다음에 실행할 명령어의 메모리 주소를 가리킴

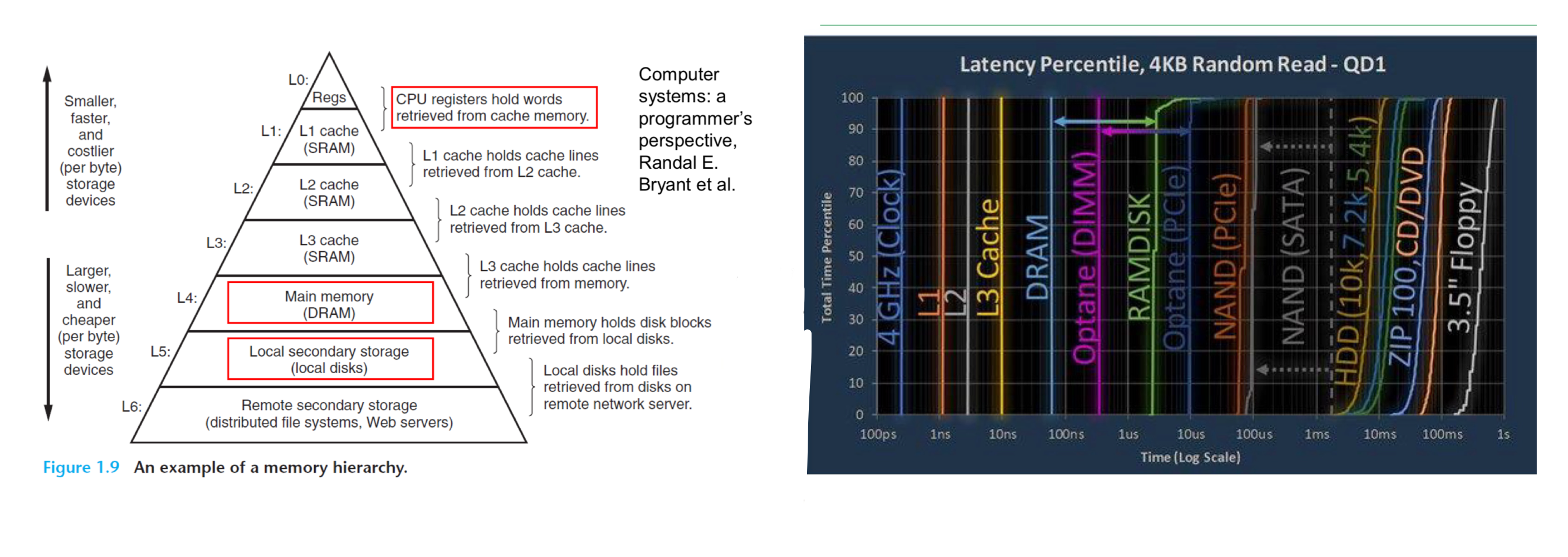

이러한 메모리는 우선 순위에 따라 Regs (Registers)로부터 L1~L3의 SRAM과 DRAM, 디스크 순으로 그 계층이 분리된다. 더 높은 계층을 가진 저장요소일수록 즉각적으로 계산되고 그 속도가 빠르다. SRAM(Static Random Access Memory)과 캐시는 CPU를 구성하고 전원이 꺼지면 정보가 소멸한다.

DRAM(Dynamic Random Access Memory)은 상대적으로 느리지만 CPU에서 계산에 필요한 이하의 모든 공간을 제공한다.

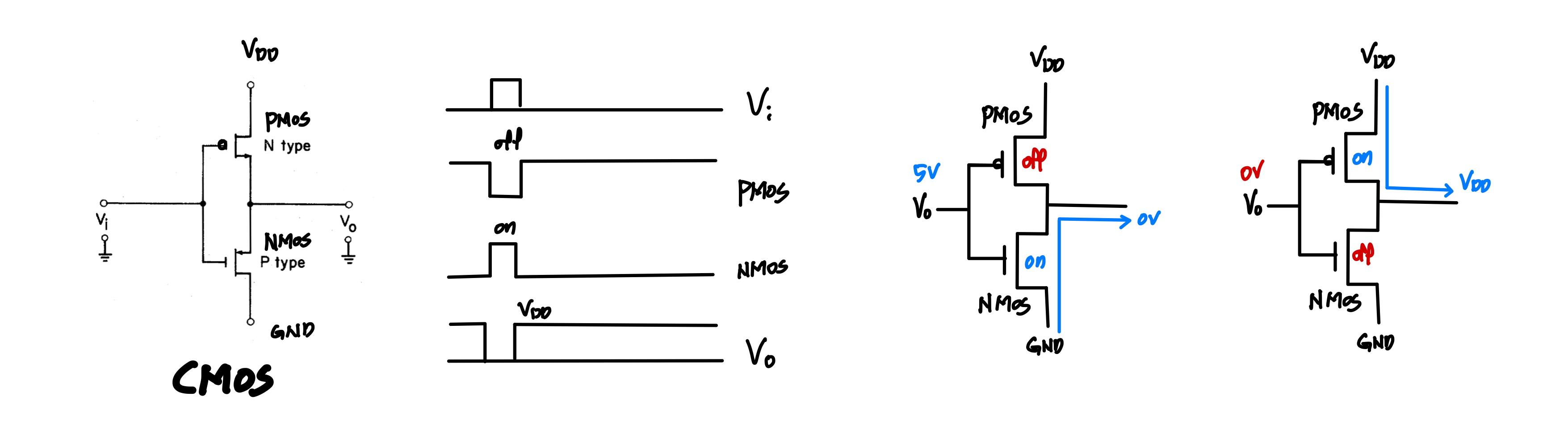

2. Basic structure and CMOS

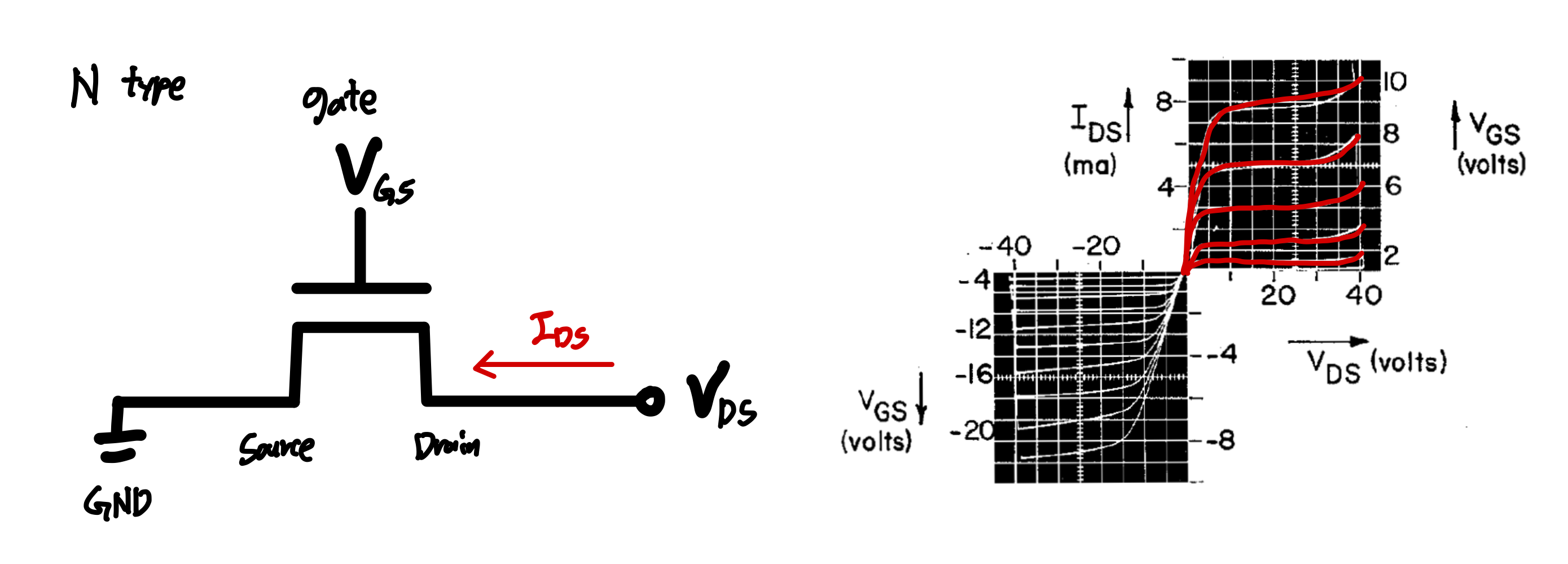

컴퓨터 연산의 기본은 트렌지스터에서 시작된다. N type Tr을 기본으로 하자면 Source에 ground가 걸리고, Drain에 +V_DS가 걸려있는데 이는 평소에 닫혀 있다. 만약 V_GS가 임계값 이상으로 전압이 가해지면 전계 효과에 의해 Drain과 Source 사이에 전류량이 늘게 되고 이것이 on 신호를 생성한다. MOS 트랜지스터의 기본 원리로 스위치 역할을 하게된다.

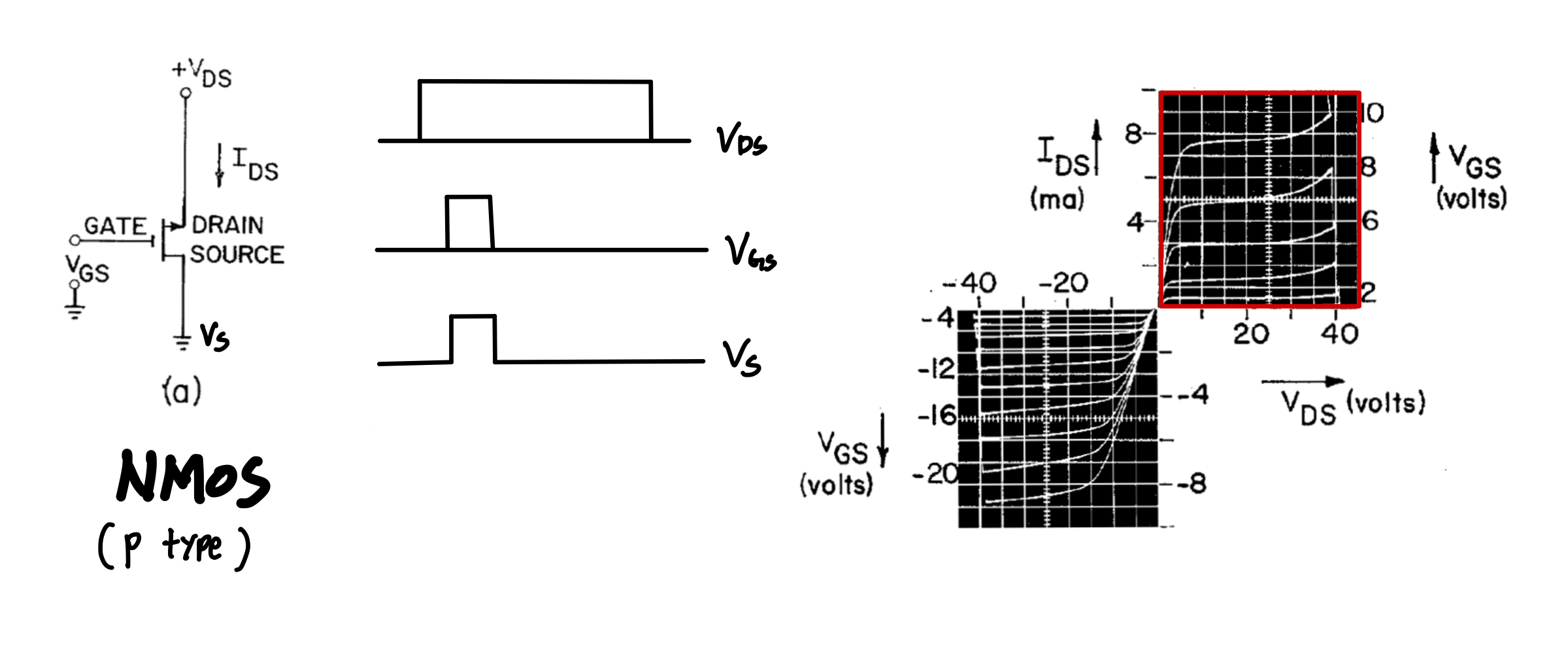

여기서 트랜지스터의 종류는 2개로 나뉘는데 기판에 p형이고 전자를 캐리어로 하는 NMOS와 기판이 n형이고 홀을 캐리어로 하는 PMOS로 크게 분류 된다.

NMOS는 게이트에 높은 전압을 가하면 산화막 아래에 반전된 n형 채널이 형성되어 전류가 흐르게 된다. 반대로 게이트 전압이 없거나 낮으면 채널이 형성되지 않아 전류는 흐르지 않게 된다. 이때 전자는 주요 캐리어로 작용하며, 그렇기에 NMOS는 VDS가 공급되었을때 gate에 전압이 걸리면 Source에 +VDS신호를 줄수 있다.

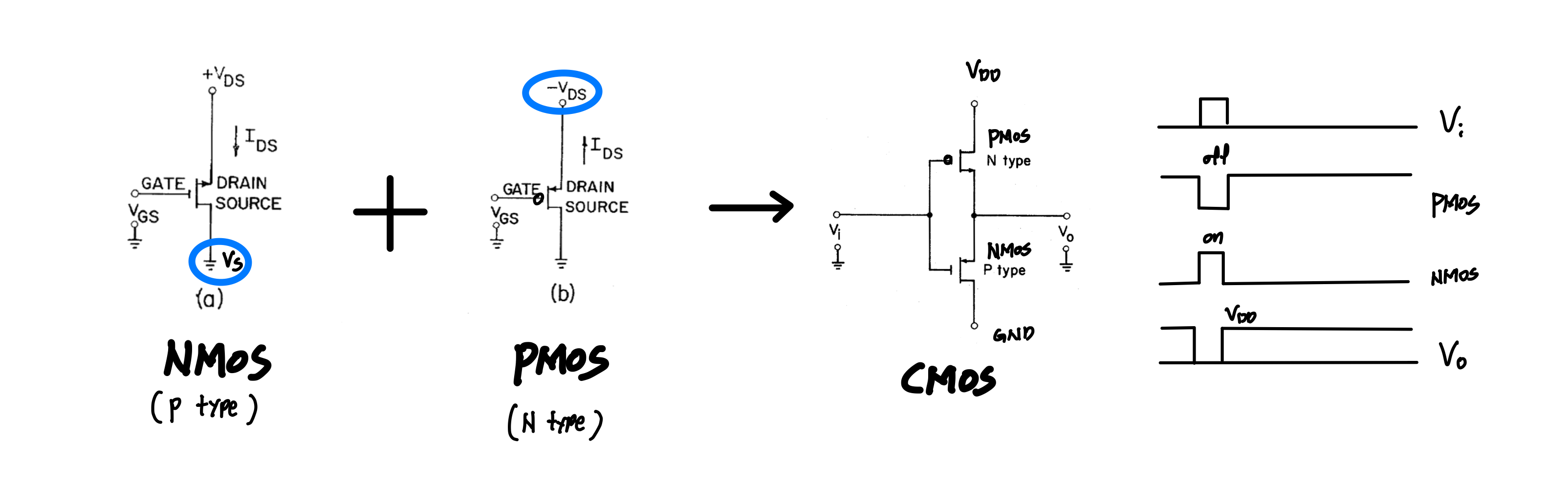

PMOS는 NMOS와 반대로 게이트에 전압을 인가하면 p형 채널이 형성되어 전류가 흐릅니다. 이때는 정공(hole)이 주요 캐리어로 작용하며, 게이트가 열리면 -VDS신호를 줄 수 있다. PMOS는 보통 전원 쪽에 위치한 High-side 스위치로 사용된다.

이러한 2가지 형태의 트랜지스터를 결합하면 서로의 장단점을 보완한 안정적인 CMOS를 만들 수 있다. 이것이 대부분의 반도체의 기본 구성요소가 된다.

NMOS와 PMOS모두 gate에 전압이 인가되면 열리지만 둘은 흘려줄수 있는 전압이 다르다. NMOS의 Vs와 PMOS의 -VDS를 연결하면 NMOS 입장에서는 반도체 전체에 가해지는 VDD 전압과 Vo를 연결받고 PMOS입장에서는 Vo로부터 GND를 연결받는다. (화살표 방향 주의!) 결국 Vi로 두 게이트에 전압이 가해지면 PMOS는 거꾸로 마치 닫히는 것처럼 (off state) 작용하고 NMOS는 열린다. 반대로 전압이 사라지면 PMOS는 열리고 NMOS는 닫힌다.

결국 CMOS는 Vi가 on이면 Vo가 off이고 그 반대도 작동한다. NMOS 반도체 하나만 구성하여 논리회로를 만들면 전압이 불안정 하지만 CMOS는 트렌지스터 2개가 서로 문을 열고 닫아주기에 V floating에서 자유롭고 안정적이다.

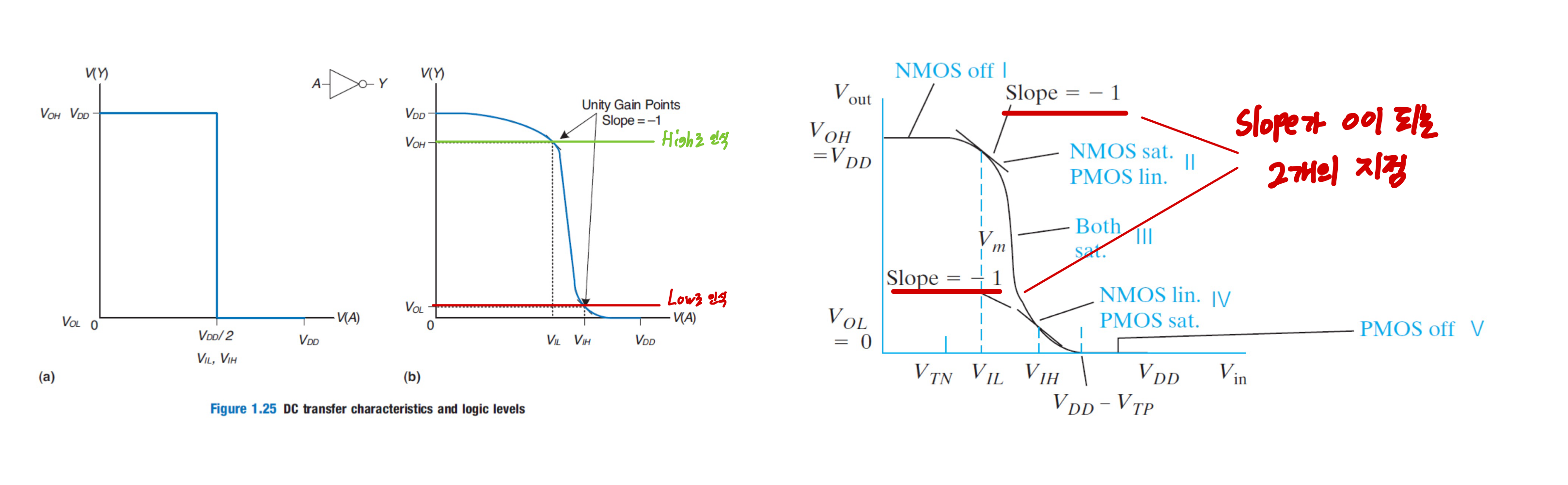

3. Voltage Transfer and Noise margin

이러한 CMOS의 on off 스펙트럼을 살펴보자. VDD/2보다 전압이 크면 (사실상의 임계전압이다) 회로가 닫혀 0이 되고 전압이 작으면 회로가 열려 1이 된다. 하지만 실제로는 이상적인 값처럼 수직하게 감소하지 않고 천천히 내려가는 곡선을 그린다.

하지만 결국 CMOS는 신호를 처리하는 회로로 사용해야 하기에 어느 임계 지점을 넘어서면 on, off로 판단짓는 선이 필요하고 그것을 high는 VOH 보다 크고, low는 VOL보다 작아야 한다고 하자.

이것은 곡선의 기울기가 -1이 되는 지점 (당연히 2개 발생)로 정의하고 그때의 값을 VOH, VOL이라고 정의하고 그 당시 게이트 전압을 VIL, VIH라고 하자.

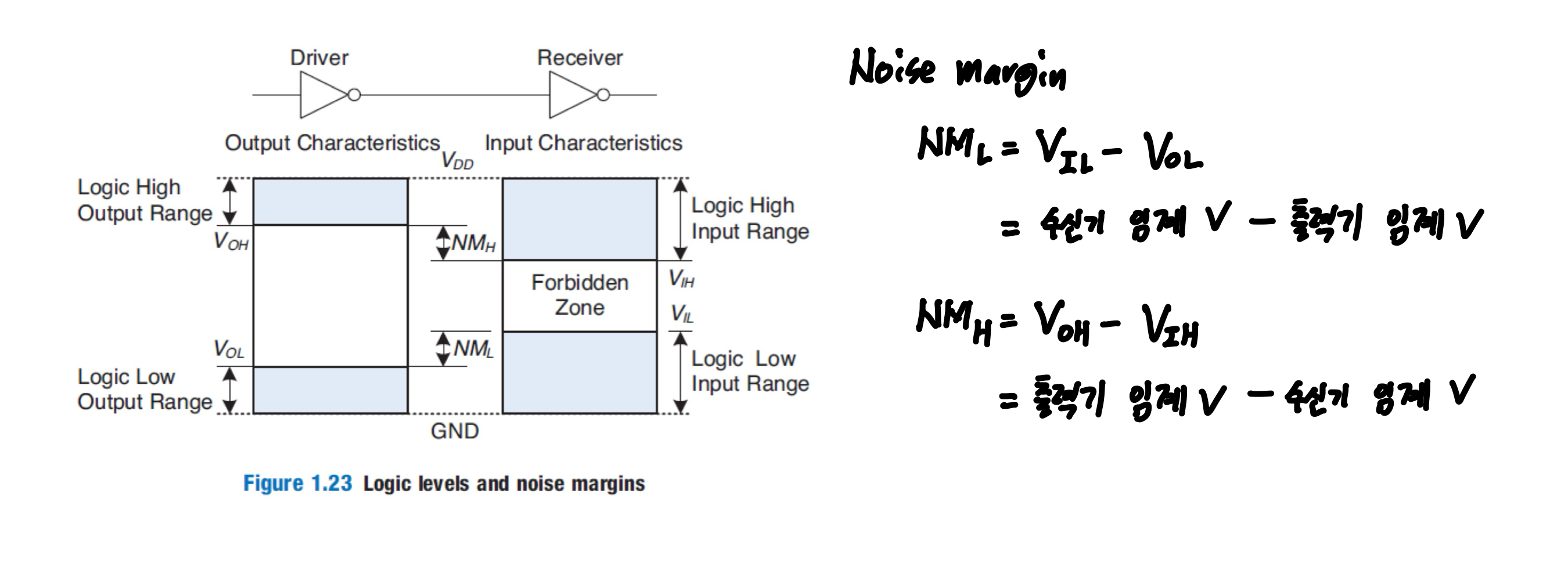

이때 신호를 주는 쪽과 신호를 받는 쪽에 입장에서 어느정도 오차를 허용할 수 있는지를 Noise Margin(NM)이라고 하고 각각 high와 low일때 다음과 같이 정의된다. 이는 output 신호기의 오차생성이 작을수록 input 신호기의 오차 허용이 클수록 커지고 위의 수식으로 설명된다.

'재료공학 > 반도체 공학' 카테고리의 다른 글

| NAND flash memory (1) | 2025.06.10 |

|---|---|

| Memory Technologies (0) | 2025.06.10 |

| Hall 측정과 Hall 계수 (0) | 2024.10.19 |

| 전류와 전기장에 의한 전자의 이동 (0) | 2024.10.19 |

| 반도체의 종류 (0) | 2022.03.11 |